substraction for negative) final operation, demote, z = int32(z) Issues: The operation must not need more than double of bits. substraction for negative) final operation, demote, z = int16(z) example 32-bit add first promote z= double(x) + double (y) note that for 32-bit z= int64(x)+ int64(y) does not work if overflow, correct the sum by substracting power(2,32) if positive (resp. Solution Use promotion example 16-bit add first promote z= int32(x) + int32 (y) if overflow, correct the sum by substracting power(2,16) if positive (resp. Matlab offers the unusual problem of having to add modulo mode to a operator working in saturated mode. Saturation is easily added to an operator working in modulo mode Example 32-bit add z = x+y overflow = xor(z.32, z.31) if (overflow) z = sat(z) as long that we have access to bit 32 (means larger width).

INTRO - MODULO vs SATURATED ARITHMETIC Matlab use saturated arithmetic Embedded in the (U)INTXX type Note that it is attached to the type not the operator.

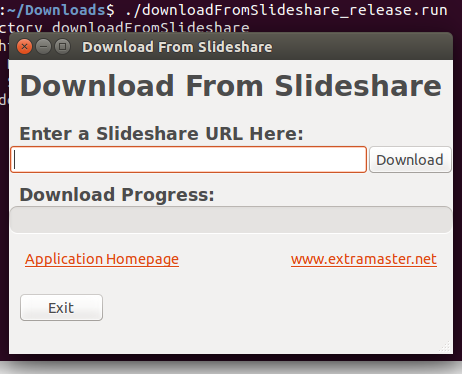

Matlab 64 bits mega slideshare free#

INTRO - Arithmetic issues and FXP problem This is the FXP perspective 3 types of modal arithmetic Modulo on overflow, wrap-around (max becomes 0) 32 + 32 32 Ex: C integer type, hardware Saturated on overflow, saturate (max+1 becomes max) 32 + 32 32 Matlab integer type (intXX) Promoted overflow is impossible (*) (*) in the limits of the precision 32 + 32 33 (width increase) Ex: Floating point (*), 8-bit data in 256-bit, free hardware Propagation Matlab: integer supersedes FP C: FP supersedes integer INTRODUCTION Arithmetic issues and FXP problem 3 modal arithmetic types propagation mode MATLAB issues Modeling concepts TWO DESIGN FLOWS Design flows Behavioral model Bit accurate model Phase accurate model Pipeline model MATLAB Powerful environment more functions than any other languages integrated from top to bottom pipedream? SIMULINK Implicit timing and concurency Access tools built directly into models easily change parameters to model the FXP effects (rounding,overflow,scaling) MATHWORKS design flow Design hierarchy Functional model Bit accurate model Time accurate model Pipeline model Tool (LANGUAGE) name MATLAB SIMULINK VERILOG Alternative names Functional: behavorial Bit accurate: bit exact Time accurate: phase accurate Pipeline: microarchitecture

Matlab 64 bits mega slideshare how to#

WHY? Typical DSP architecture issues How much parallelism? multi-lane (2,4,8,16) study How wide? Bit exact hardware, near-bit exact hardware MAC operator multiple units mixing rounding and saturation refer to ITU library (all single, all serial) Compound operators how to deal with multiple overflow? where to do saturation? Complex (as in A+iB) operators DSP Functions where? Coprocessing issues MATLAB specific functions How? when?

TUTORIAL PROGRESS DSPMA1 overview of typical issues VNEG any type FXP uses INTxx any shape vector, introduction to VU exercise: NEG modulo ADD2 MODULO we cover how to do modulo FUSED ADDERS more into parallelism ACCUMARRAY some architecture issues interesting problems DIFF to do VPU internal sequencer IIR1 introduction to all filters states PMAVF256: massive parallelism PPT TEMPLATE Design hierarchy Functional model level 3 is 20 Bit accurate model Time accurate model Pipeline model DSP CPU Architecture Modelling with Matlab WHY? DESIGN FLOW INTRODUCTION FXP Issues MATLAB ISSUES Modeling Terms & Definitions TUTORIAL PROGRESS DSPMA1 VNEG ADD2 MODULO FUSED ADDERS ACCUMARRAY DIFF VPU DESIGN FILTER DESIGN (IIR1,PMAVF256, LMS,NLMS) EQUALIZER

0 kommentar(er)

0 kommentar(er)